來源:壹芯微 發(fā)布日期

2020-12-15 瀏覽:-

來源:壹芯微 發(fā)布日期

2020-12-15 瀏覽:-MOS管知識解析|要如何降低MOS的失效率

如何以最小代價降低MOS的失效率

如何降低MOS的失效率:在高端MOS的柵極驅動電路中,自舉電路因技術簡單、成本低廉得到了廣泛的應用。然而在實際應用中,MOS常莫名其妙的失效,有時還伴隨著驅動IC的損壞。如何解決?一個合適的電阻就可搞定問題。

【問題分析】

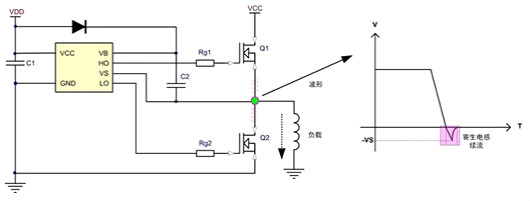

圖為典型的半橋自舉驅動電路,由于寄生電感的存在,在高端MOS關閉后,低端MOS的體二極管鉗位之前,寄生電感通過低端二極管進行續(xù)流,導致VS端產生負壓,且負壓的大小與寄生電感與成正比關系。

該負壓會把驅動的電位拉到負電位,導致驅動電路異常,還可能讓自舉電容過充電導致驅動電路或者柵極損壞。由于IC的驅動端通常都有寄生二極管,當瞬間的大電流流過驅動口的二極管時,很可能引發(fā)寄生SCR閉鎖效應,導致驅動電路徹底損壞。

【解決方法】

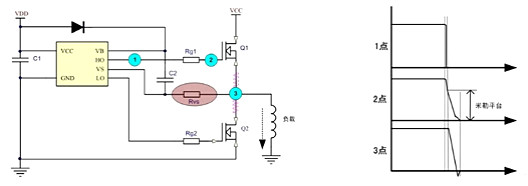

如何降低MOS的失效率:如上圖所示,在自舉驅動芯片VS端與Q1的源極之間增加一個電阻Rvs,該電阻不僅是自舉限流電阻,同時還是導通電阻和關斷電阻。

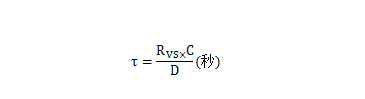

由于占空比受自舉電容影響,該電阻值一般不能取得較大,推薦值為3~10Ω較為適宜。電阻和自舉電容的容值與其充電時間可以由以下公式得出:

其中C是自舉電容容值,D為最大占空比

對于減小高端MOS驅動的寄生振蕩,除通過增加驅動端的電阻發(fā)揮作用外,在印制電路板的設計中,還可注意以下一些細節(jié),將寄生振蕩降到最低。

如:自舉二極管應緊靠自舉電容,功率布線盡量短且走線圓滑,直插器件應緊貼PCB以減小寄生電感等。

壹芯微科技針對二三極管,MOS管作出了良好的性能測試,應用各大領域,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

工廠地址:安徽省六安市金寨產業(yè)園區(qū)

深圳辦事處地址:深圳市福田區(qū)寶華大廈A1428

中山辦事處地址:中山市古鎮(zhèn)長安燈飾配件城C棟11卡

杭州辦事處:杭州市西湖區(qū)文三西路118號杭州電子商務大廈6層B座

電話:13534146615

企業(yè)QQ:2881579535

深圳市壹芯微科技有限公司 版權所有 | 備案號:粵ICP備2020121154號