來源:壹芯微 發布日期

2021-12-15 瀏覽:-

來源:壹芯微 發布日期

2021-12-15 瀏覽:-基于FPGA的可重構密碼芯片設計介紹

目前,國內外廣泛使用的密碼處理芯片大都是實現某種特定密碼算法的專用芯片,如MD5芯片、SHA一1芯片等。由于專用密碼芯片實現的密碼算法是確定的且不可更改的,因此難以滿足不同密碼用戶多層次的安全性需要。為克服這一缺陷,本文介紹了SHA一1、SHA224及SHA256三種安全雜湊算法的基本流程,采用可重構體系結構的設計思想和方法設計出一款可實現這三種算法的可重構密碼芯片,并對關鍵路徑進行了優化設計。最后給出了基于Ahera公司的Cyclone系列FPGA的可重構密碼芯片的實現結果。

1.算法簡介

1.1SHA-1算法介紹

SHA-1算法輸入報文的最大長度不超過264bit,輸入按512bit分組進行處理,產生的輸出是一個160bit的報文摘要。該算法處理包括以下幾個步驟:

(1)附加填充比特。對報文進行填充使報文長度與448模512同余(長度=48 mod 512),填充的比特數范圍從1到512,填充比特串的最高位為1,其余位為0。

(2)附加長度值。將用64bit表示的初始報文(填充前)的位長度附加在步驟(1)的結果后(低位字節優先)。

(3)初始化緩存。使用一個160bit的緩存存放該散列函數的中間值及最終結果。該緩存的值分別表示為A=67452301。B=EFCDAB89,C=0x98BADCEF,D=0x10325476,E=C3D2E1F0。

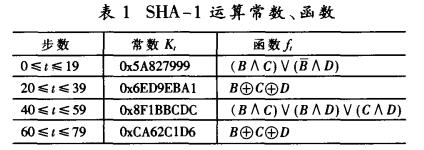

(4)處理512bit(16個字)報文分組序列。算法的核心是一個包含四個循環的模塊,每個循環由20個處理步驟組成。四個循環有相似的結構,但每個循環使用不同的邏輯函數,分別表示為f1、f2、f3、f4。每個循環都以當前正在處理的512bit和160-bit緩存值A、B、C、D、E為輸入,然后更新緩存內容。每個循環還使用一個額外的常數值,對應的四輪Kt取值及邏輯函數ft如表1所示。第四循環最后一步的輸出與第一循環的輸入進行模232相加后得到下一個512bit分組計算所需的A、B、C、D、E值。

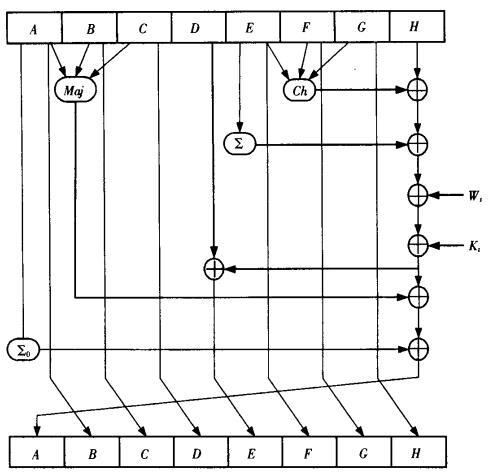

(5)所有的512bit分組處理完畢后,最后一個分組產生的輸出便是160bit的報文摘要。圖1說明了SHA一1算法中每一處理步驟所包含的操作。

圖1 基本的SHA-1操作(單步)

1.2SHA-224/SHA-256算法介紹

SHA-224/SHA-256算法輸入報文的最大長度不超過264bit,輸入按512bit分組進行處理,產生的輸出是一個224bit或256bit的報文摘要。該算法處理包括以下幾個步驟:

(1)和(2)與SHA-1算法的前兩步相同。

(3)初始化緩存。使用一個256bit的緩存存放該散列函數的中間值及最終結果。當執行SHA-224算法時,該緩存的值分別表示為A=0xC1059ED8,B=0x367CD507,C=0x3070DD17,D=0xF70E5939,E=0xFFC00B31,F=0x68581511,G=0x64F98FA7,H=0xBEFA4FA4;當執行SHA一256算法時,該緩存的值分別表示為:A=0x6A09E667=0xBB67AE85,C=0x3C6EF372,D=0xA54FF53A,E=0x510E527F,F=0x9B05688C,G=0x1F83D9AB,H=0x5BEOCD19。

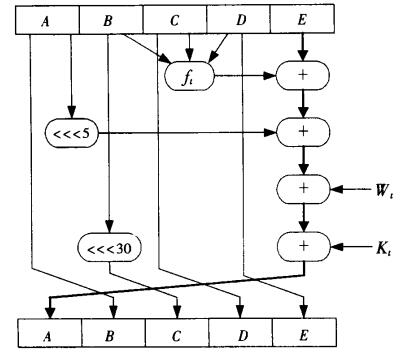

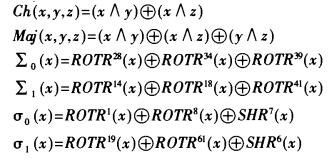

(4)處理512bit(16個字)報文分組序列。該算法使用六種基本邏輯函數,由64步迭代運算組成。每步都以256bit緩存值A、B、C、D、E、F、G、H為輸入,然后更新緩存內容。每步使用一個32bit常數值Kt和一個32bitWt。六種基本函數如下:

Wt是由當前的輸入分組(512bit長)導出的32bit長的數。在所有64次運算完成之后,將其輸出A、B、C、D、E、F、G、H與第一步的輸入A、B、C、D、E、F、G、H的值對應進行模232相加。然后將其結果作為下一分組數據A、B、C、D、E、F、G、H的值繼續運行算法。

(5)所有的512bit分組處理完畢后,對于SHA256算法,最后一個分組產生的輸出便是256bit的報文摘要;若是SHA-224算法,則最后一個分組產生的輸出取前224bit作為報文摘要。圖2說明了SHA-224/SHA-256算法每一處理步驟所包含的操作。

圖2 基本的SHA-224/SHA-256單步運算

2.電路結構

2.1總體結構設計

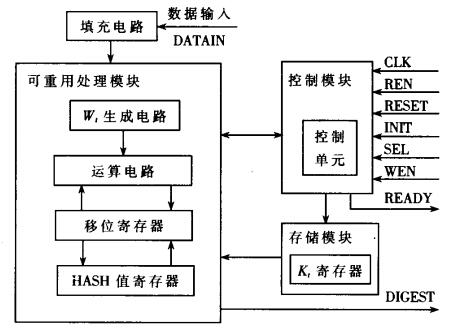

本設計采用可重構密碼芯片的設計思想,通過對SHA-1、SHA-224、SHA-256三種算法分析可以看出,這三種算法的Wt生成電路和移位存儲模塊是可重用的部件。數據通路中的CSA加法器、存放雜湊值的移位寄存器以及常數值存儲模塊K也都是可重用的部件。按照上述分析,把該芯片分為三大模塊:存儲模塊、控制模塊、可重用處理模塊。其中,存儲模塊用于存儲各種算法所需的常數值。控制模塊用于接收外部的控制信號和選擇算法信號,控制各種算法的存儲和運算。可重用處理模塊用于對各種算法進行可重構計算。根據整體算法要求,又將其再往下劃分為七個功能子模塊。本設計充分利用FPGA可重構計算的特點,對可重用的模塊進行可重構計算以實現對FPGA資源的靈活有效利用。SHA-1/SHA-224/SHA-256可重構運算電路IPCORE由以下七個子模塊構成:控制電路、Wt生成電路、Kt常數寄存器、填充電路、運算電路、HASH值暫存寄存器、移位寄存器。本設計總體結構框圖如圖3所示。

圖3 SHA-1/SHA-224/SHA-256可重構芯片電路設計整體架構

其中,Kt常數寄存器子模塊和HASH值暫存寄存器子模塊屬于存儲模塊;Wt生成電路子模塊、填充電路子模塊、運算電路子模塊、移位寄存器子模塊屬于可重用處理模塊。控制電路子模塊屬于控制模塊。每個子模塊具體功能為:Wt生成電路負責對每組512bit的輸入數據生成64個或80個32bit的字并送入運算通路。Kt常數寄存器用于存儲64個或80個32bit的常量。控制電路負責接收外部的控制信號,并產生所有的內部控制信號,采用計數器電路生成。填充電路接收輸入數據,產生每個512bit分組并送入Wt生成電路。運算電路負責計算多個模232加法。然后將其結果送入移位寄存器。HASH值暫存寄存器用于存儲5個或8個32bit寄存器的初始值以及每個512bit分組運算完畢后的5個或8個32bit寄存器的臨時值。移位寄存器負責對每步運算的數據進行移位存儲。當HASH運算結束時,移位寄存器將其本身值與HASH值暫存寄存器中的值相加。當外部讀信號有效時,電路實現串行移位功能,在控制信號作用下,將寄存器內的數據順序讀出。

CLK是系統時鐘信號;RESET是復位信號,RESET有效時,所有寄存器復位;INIT是初始化信號,INIT有效時,初始化摘要計算,在每一批數據進行摘要運算之前,首先執行初始化操作,然后按512bit分組寫入數據;WEN是寫使能信號,WEN有效時,在CLK時鐘上升沿將512bit的數據分16次由32bit數據總線寫入芯片內部數據寄存器;REN是讀使能信號,REN有效時,將內部運算結果讀出數據端口;DATAIN是數據輸入,即輸入的512bit分組數據。SEL是選擇算法指令信號,用來選擇所需的算法。READY是運算狀態信號,每512bit分組運算完畢后,READY變為有效,等待讀出或外部數據繼續輸入。DIGEST是摘要值輸出,即REN信號有效時輸出的相應摘要值。

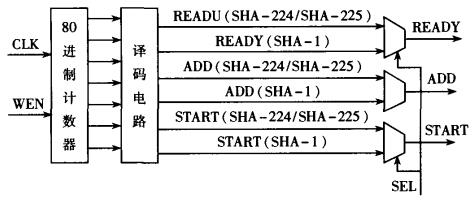

2.2控制電路設計

控制電路的核心是一個7位計數器,每來一個時鐘信號,便進行加1操作,根據不同的計數值可給出不同的控制信號。依照算法要求,每處理一組5l2bit分組數據時,若執行SHA-1算法則需要80步運算;若執行SHA-224/SHA-256算法則需要64步。為實現邏輯資源的可重構,達到計數器資源重用的目的,就需要計數器在不同的算法下產生不同的控制信號。本控制電路采用增加選擇算法信號(SEL)來實現,其結構如圖4所示。其中READY信號表示每一分組運算完成信號。ADD信號表示分組運算的最后一步各寄存器的值與第一步計算時的各寄存器的輸入值相加信號。START信號表示移位寄存器移位信號。

圖4 SHA-1/SHA-224/SHA-256控制電路設計

2.3數據路徑優化設計

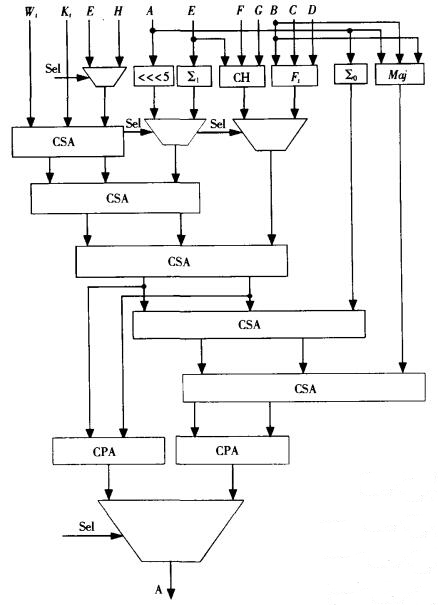

SHA-1運算模塊使用五個寄存器(見圖1)存放散列函數每一步運算的中間結果;SHA-224/SHA-256運算模塊則采用八個寄存器(見圖2)存放散列函數每一步運算的中間結果。為實現可重構計算以使不同算法邏輯單元重用,本設計采用八級移位寄存器A、B、C、D、E、F、G、H實現,每個寄存器32bit位寬。當執行SHA一1算法時,使用前五個32bit移位寄存器;當執行SHA-224/SHA-256算法時,使用全部八個移位寄存器。當RESET信號有效時,寄存器初始化,電路將根據不同算法給寄存器賦初值。數據路徑設計的關鍵是計算每步A寄存器的值。當執行SHA-1算法時,At+1=(Et+ft(Bt,Ct,Dt)+At(<<<5)+Wt+Kt)mod232;當執行SHA-224/SHA-256算法時:At+1=(Ht+∑t(Et)+Ch(Et,Ft,Gt)+Kt+Wt+∑0(At)+Maj(At,Bt,Ct)mod232

式中:At、Bt、Ct、Dt、Et、Ft、Gt、Ht、Wt、Kt是第t時刻的各寄存器的值、消息分組和常數值。At+1是第t+1時刻的A寄存器的值。

SHA-1/SHA-224/SHA-256運算模塊的關鍵路徑的設計是計算At+1,在這一路徑中,需要完成多個多變量邏輯函數和多個連續32位加法的運算。可以看出,At+1計算主要包括非線性函數運算、加法運算和移位。其中非線性函數運算只是完成信號在不同輸入輸出之間的切換,只需用組合邏輯電路設計,不會產生太大的延遲;移位只占用布線資源,同樣不會對電路的速度有影響;而加法運算由于進位會在電路上產生延遲,因此應盡量對其進行優化,否則會影響電路運算速度。因此在電路的設計上采用保存進位加法器(CSA),以減少延遲。由于SHA-1算法執行的是五個連續32位加法,而SHA-224/SHA-256執行的是七個連續32位加法,而且SHA-1與SHA-224/SHA-256所使用的邏輯函數和輸入寄存器的值不同,這就需要將各個不同的函數變換的值提前計算出來,再根據選擇的算法對不同的值進行選擇,然后送入CSA加法器的輸入端。

本設計電路由五級保存進位加法器(CSA)和兩個串行進位加法器(CPA)構成,實現了保存進位加法器對不同算法的重用,其結構如圖5所示。

圖5 連加運算優化電路

3.性能評估

以上設計采用VHDL語言描述,在QuartusII 4.2環境下編譯綜合,選用Altera Cyclone系列器件為目標器件進行整體綜合、仿真和底層布局,采用FIPS180-2給出的測試數據進行仿真,采用單個分組和多個分組分別進行測試,均得到正確結果。

在本設計中,當電路執行SHA-1算法時運算一個512bit分組需要82個時鐘周期,其中第一個為數據準備周期,第2~81個為運算周期,第82個為移位寄存器的值與HASH值暫存寄存器的值相加并將其結果送入移位寄存器的周期;當執行SHA-224/SHA-256算法時運算一個512bit分組需要66個時鐘周期,其中第一個為數據準備周期,第2~65個周期為運算周期,第66為移位寄存器的值與HASH值暫存寄存器的值相加并將其結果送入移位寄存器的周期。該模塊的運算速度可以通過下面公式得出:

運算速度=(分組長度/運算耗用的時鐘周期數)×系統時鐘頻率,單位為Mbps

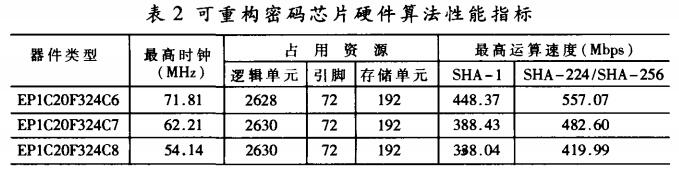

將實現的可重構算法分別下載到Altera Cyclone系列器件后測得的主要性能指標在表2中給出。

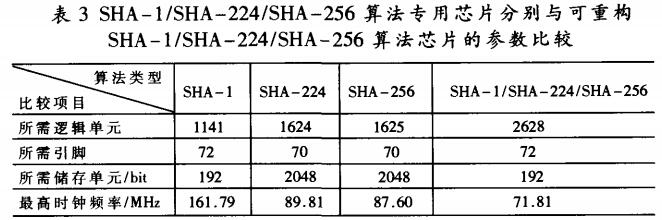

本設計的創新點是利用可重構設計思想對SHA-1、SHA-224、SHA-256三種不同算法的可重用模塊進行可重構計算,通過FPGA實現時既能靈活實現不同算法,又能實現資源的充分利用,節約大量邏輯資源。為進一步說明本設計對FPGA資源利用情況,下面將這三種算法的專用芯片與可重構SHA-1/SHA-224/SHA-256算法芯片的一些參數進行比較,如表3所示。這里要說明的是這三種算法的參數均是采用類似SHA-1/SHA-224/SHA-256的總體電路架構設計得到的。選擇的器件均是EP1C20F324C6。

結束語

本文總結了基于FPGA的可重構密碼芯片設計方案。該可重構密碼芯片是一種創新性的密碼芯片,它很好地克服了傳統的密碼芯片只能實現特定密碼算法的弊端,使得密碼使用者能夠在它上面很方便地選擇所需要的密碼算法,從而大大提高了密碼系統的靈活性。可重構密碼芯片可作為構建密碼系統的核心部件而廣泛應用于保密通信、網絡終端加密設備等領域,因此該研究方向具有重要的政治、軍事和經濟意義。

〔壹芯微〕國內功率半導體制造廠商,主營各類貼片與直插,二極管、三極管、MOS(場效應管)、可控硅、三端穩壓管、整流橋,IC(集成電路);參數達標,質量保障,工廠直銷(價省20%),免費送樣,選型替代,技術支持,專業售后,如需了解產品詳情或最新報價,歡迎咨詢官網在線客服。

手機號/微信:13534146615

QQ:2881579535(點擊可咨詢)

工廠地址:安徽省六安市金寨產業園區

深圳辦事處地址:深圳市福田區寶華大廈A1428

中山辦事處地址:中山市古鎮長安燈飾配件城C棟11卡

杭州辦事處:杭州市西湖區文三西路118號杭州電子商務大廈6層B座

電話:13534146615

企業QQ:2881579535

深圳市壹芯微科技有限公司 版權所有 | 備案號:粵ICP備2020121154號