收藏壹芯微 | 在線留言| 網(wǎng)站地圖

您好!歡迎光臨壹芯微科技品牌官網(wǎng)收藏壹芯微 | 在線留言| 網(wǎng)站地圖

您好!歡迎光臨壹芯微科技品牌官網(wǎng) 來源:壹芯微 發(fā)布日期

2020-08-10 瀏覽:-

來源:壹芯微 發(fā)布日期

2020-08-10 瀏覽:-集成電路設(shè)計(jì)知識(shí)概括

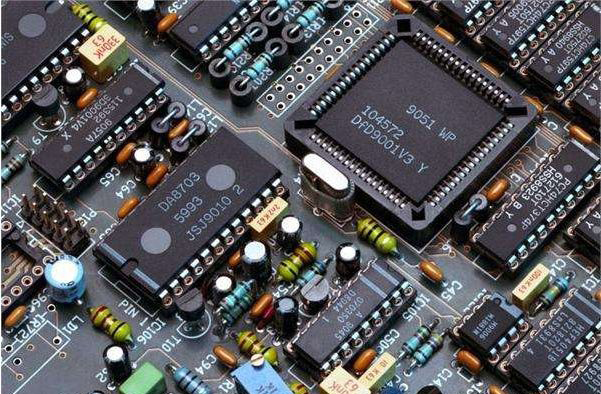

集成電路設(shè)計(jì),一般英文稱為IC,integrated circuit;集成電路設(shè)計(jì)可以分為很多方面,主要包括模擬電路設(shè)計(jì)和數(shù)字集成電路設(shè)計(jì),模擬集成電路設(shè)計(jì)可以分為射頻集成電路設(shè)計(jì)和普通的模擬集成電路設(shè)計(jì),一般模擬電路設(shè)計(jì)需要工程師對(duì)工藝的了解要很深;數(shù)字集成電路主要是針對(duì)崗位,有做系統(tǒng)的,有做具體的IP的,還有coder是RTL實(shí)現(xiàn)的,這是一種分類方法,還有就是根據(jù)做的項(xiàng)目的種類是做ASIC或者是MCU等,當(dāng)然這時(shí)候就不是單純的數(shù)字電路設(shè)計(jì)了;除了這兩種還有一種是做電源設(shè)計(jì)的,對(duì)工藝了解的要求基本上是最高的了。

集成電路設(shè)計(jì)根據(jù)具體的項(xiàng)目會(huì)有不同的實(shí)現(xiàn)途徑。比如說單獨(dú)的模擬電路芯片板塊,這時(shí)候前期模擬電路設(shè)計(jì)人員根據(jù)具體的要求指標(biāo)設(shè)計(jì)電路(選擇器件類型);電路功能實(shí)現(xiàn)后交于后端工程師進(jìn)行版圖設(shè)計(jì),不過有時(shí)候是電路設(shè)計(jì)人員自己設(shè)計(jì)版圖;版圖實(shí)現(xiàn)后選定封裝策略,根據(jù)具體芯片運(yùn)行環(huán)境選擇;然后進(jìn)行測試,測試不成功則需要找出原因,返回之前的步驟反復(fù)進(jìn)行。

一般現(xiàn)在常用的集成電路設(shè)計(jì)的流程先要進(jìn)行軟硬件的劃分,將設(shè)計(jì)基本分為兩部分:芯片硬件設(shè)計(jì)和軟件協(xié)同設(shè)計(jì)。

芯片硬件設(shè)計(jì)包括:

1.功能設(shè)計(jì)階段。 設(shè)計(jì)人員產(chǎn)品的應(yīng)用場合,設(shè)定一些諸如功能、操作速度、接口規(guī)格、環(huán)境溫度及消耗功率等規(guī)格,以做為將來電路設(shè)計(jì)時(shí)的依據(jù)。更可進(jìn)一步規(guī)劃軟件模塊及硬件模塊該如何劃分,哪些功能該整合于SOC 內(nèi),哪些功能可以設(shè)計(jì)在電路板上。

2.設(shè)計(jì)描述和行為級(jí)驗(yàn)證供能設(shè)計(jì)完成后,可以依據(jù)功能將SOC 劃分為若干功能模塊,并決定實(shí)現(xiàn)這些功能將要使用的IP 核。此階段將接影響了SOC 內(nèi)部的架構(gòu)及各模塊間互動(dòng)的訊號(hào),及未來產(chǎn)品的可靠性。決定模塊之后,可以用VHDL 或Verilog 等硬件描述語言實(shí)現(xiàn)各模塊的設(shè)計(jì)。接著,利用VHDL 或Verilog 的電路仿真器,對(duì)設(shè)計(jì)進(jìn)行功能驗(yàn)證(functionsimulation,或行為驗(yàn)證 behavioral simulation)。注意,這種功能仿真沒有考慮電路實(shí)際的延遲,但無法獲得精確的結(jié)果。

3.邏輯綜合確定設(shè)計(jì)描述正確后,可以使用邏輯綜合工具(synthesizer)進(jìn)行綜合。綜合過程中,需要選擇適當(dāng)?shù)倪壿嬈骷?logic cell library),作為合成邏輯電路時(shí)的參考依據(jù)。硬件語言設(shè)計(jì)描述文件的編寫風(fēng)格是決定綜合工具執(zhí)行效率的一個(gè)重要因素。事實(shí)上,綜合工具支持的HDL 語法均是有限的,一些過于抽象的語法只適于作為系統(tǒng)評(píng)估時(shí)的仿真模型,而不能被綜合工具接受邏輯綜合得到門級(jí)網(wǎng)表。

4.門級(jí)驗(yàn)證(Gate-Level Netlist Verification) 門級(jí)功能驗(yàn)證是寄存器傳輸級(jí)驗(yàn)證。主要的工作是要確認(rèn)經(jīng)綜合后的電路是否符合功能需求,該工作一般利用門電路級(jí)驗(yàn)證工具完成。注意,此階段仿真需要考慮門電路的延遲。

5.布局和布線布局指將設(shè)計(jì)好的功能模塊合理地安排在芯片上,規(guī)劃好它們的位置。布線則指完成各模塊之間互連的連線。注意,各模塊之間的連線通常比較長,因此,產(chǎn)生的延遲會(huì)嚴(yán)重影響SOC的性能,尤其在0.25 微米制程以上,這種現(xiàn)象更為顯著。

壹芯微科技針對(duì)二三極管,MOS管作出了良好的性能測試,應(yīng)用各大領(lǐng)域,如果您有遇到什么需要幫助解決的,可以點(diǎn)擊右邊的工程師,或者點(diǎn)擊銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

壹芯微首頁 場效應(yīng)管 貼片二極管 榮譽(yù)認(rèn)證 直插二極管 網(wǎng)站地圖 三極管 聯(lián)系壹芯微

工廠地址:安徽省六安市金寨產(chǎn)業(yè)園區(qū)

深圳辦事處地址:深圳市福田區(qū)寶華大廈A1428

中山辦事處地址:中山市古鎮(zhèn)長安燈飾配件城C棟11卡

杭州辦事處:杭州市西湖區(qū)文三西路118號(hào)杭州電子商務(wù)大廈6層B座

電話:13534146615

企業(yè)QQ:2881579535

深圳市壹芯微科技有限公司 版權(quán)所有 | 備案號(hào):粵ICP備2020121154號(hào)