來源:壹芯微 發布日期

2022-08-31 瀏覽:-

來源:壹芯微 發布日期

2022-08-31 瀏覽:-最簡化模型分析

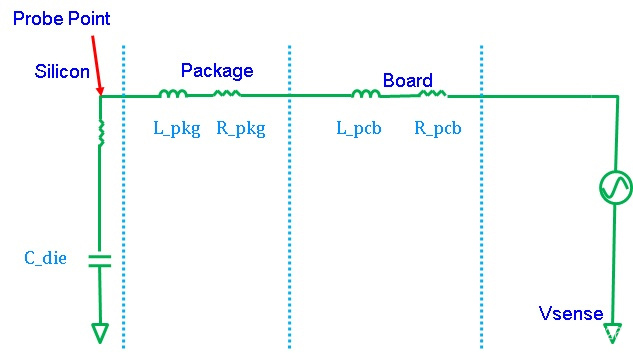

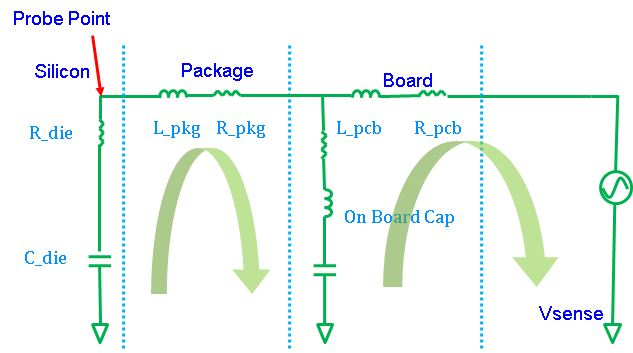

最初的芯片功能相對來說比較簡單,運行的頻率也比較低,所以也很少出現電源完整性問題。當時的工程師也很少考慮電源完整性相關的設計。我們可以使用下圖所示的PDN網絡模型來分析早期比較簡單的芯片。

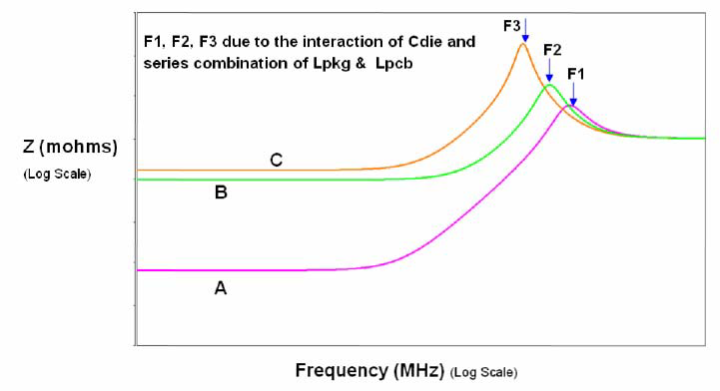

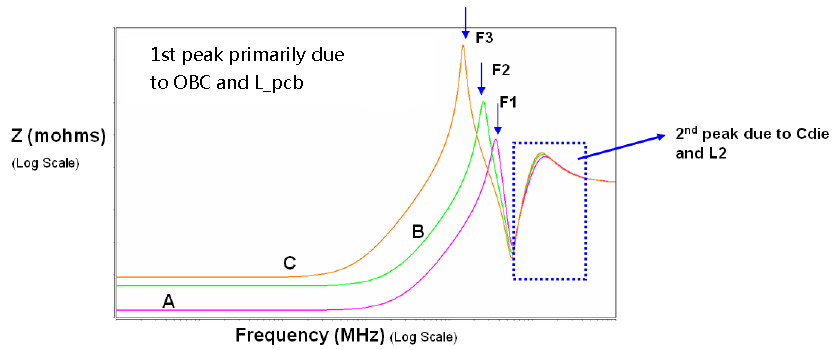

可以看到早期的芯片,并沒有在封裝上設計去耦電容。在這個模型中,die包含寄生電阻R_{die}和寄生電容C_{die},封裝包含了寄生電感L_{pkg}。同時PCB上也沒有設計去耦電容以及電源平面。這是一個典型的平行諧振電路,并行諧振電路存在并行諧振點。下圖顯示了從上圖的測試點看到的阻抗曲線。

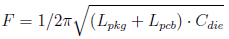

通過如下公式我們可以計算諧振頻率。

上圖同時顯示了諧振頻率與電感的關系。圖中曲線A是在R_{pcb}和L_{pcb}都為0時的阻抗曲線,此時的并行諧振頻率為F1.這個例子展示的是完全理想的PCB,沒有任何的寄生參數。

圖中曲線B是表征了在比較低的PCB寄生參數情況下的阻抗曲線,此時的并行諧振頻率為F2.此時PCB有比較低的寄生電感和寄生電阻。從圖中可以看出,阻抗的峰值向左(低頻)移動,同時峰值的幅度也有所增大。增加的PCB寄生電阻使得整個阻抗曲線都向上移動。

圖中曲線C表征的是高PCB寄生參數時的阻抗曲線,此時PCB有比較高的寄生電感和寄生電阻。此時的阻抗峰值向更加低頻方向移動,而且峰值幅度進一步提高。整個曲線的阻抗也得到了提高。

添加PCB上電容模型分析

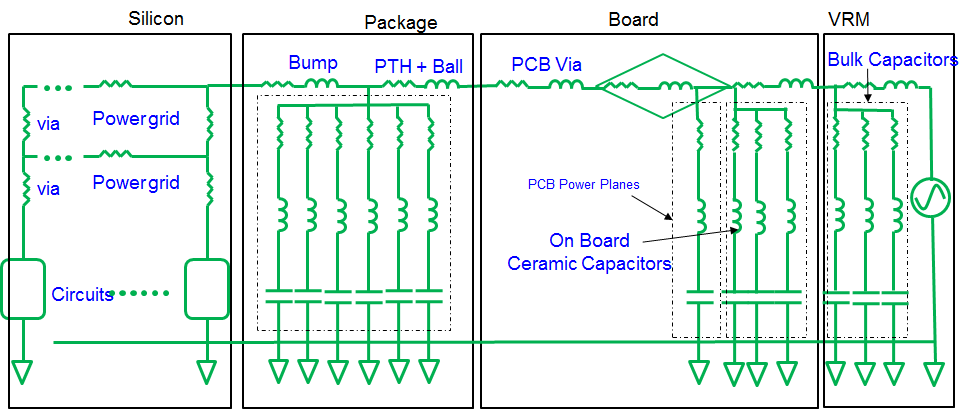

隨著芯片功能越來越復雜,需要消耗越來越多的電流,同時芯片的運行頻率也不斷的提高,在一些系統中,工程師開始在PCB上添加去耦電容。當PDN網絡中添加PCB上去耦電容以后,PDN網絡的模型變為如下圖所示。

下圖顯示了從上圖測試點看到的阻抗曲線。靠右邊的第二個阻抗峰值是由die上的電容和從die到PCB的串聯寄生電感相互作用產生的。第一個阻抗封裝是由PCB上的去耦電容和PCB傳播電感之間作用形成的。

上圖顯示了如下三種情況下的仿真結果:

理想PCB情況下的阻抗曲線

低寄生參數下的阻抗曲線

高寄生參數下的阻抗曲線

這種情況就是我們現在大量采用的wire bond封裝芯片的電源分布網絡簡化拓撲圖。通過上面的分析我們可以得到以下幾點結論:

1.由片上電容與die到PCB這段電感組成了第一個LOOP,這個loop的有一個特征諧振頻率。而這個諧振頻率主要受到片上電容以及die到PCB的寄生電感的影響。PCB上的去耦電容數量,大小等對這個諧振頻率影響很小。但是PCB上的去耦電容的位置會影響到該諧振頻率,我們需要盡量將去耦電容放置到靠近芯片的電源管腳的位置,這樣可以減小die與PCB上去耦電容之間的寄生電感。

2. PCB板上電容與PCB上寄生電感形成第二個LOOP,這個LOOP的諧振頻率受到芯片電源管腳附近的去耦電容容值,以及去耦電容與VRM之間傳輸通道的寄生電感影響。

2.諧振頻率點的左側主要表現為容性特性,右側主要變現為感性特性。也就是說如果增加去耦電容,諧振頻率會變高。如果寄生電感變大,則諧振頻率會變低。

添加封裝上電容模型分析

隨著芯片瞬態電流的不斷增大,我們需要進一步降低PDN網絡的阻抗。但是根據前面的分析,die與PCB之間的電感無法做到足夠低響很小,這時很多公司在封裝上添加去耦電容,將第一個比較大的LOOP分割成2個較小的LOOP。這樣使得第一個LOOP減小,LOOP1的寄生電感大幅減小,這樣會使得第一個諧振頻率向高頻移動,同時會降低諧振頻率附近的阻抗。

當我們講PCB上電容以及VRM都考慮進去,就會得到一個完整的PDN模型,如下圖所示。

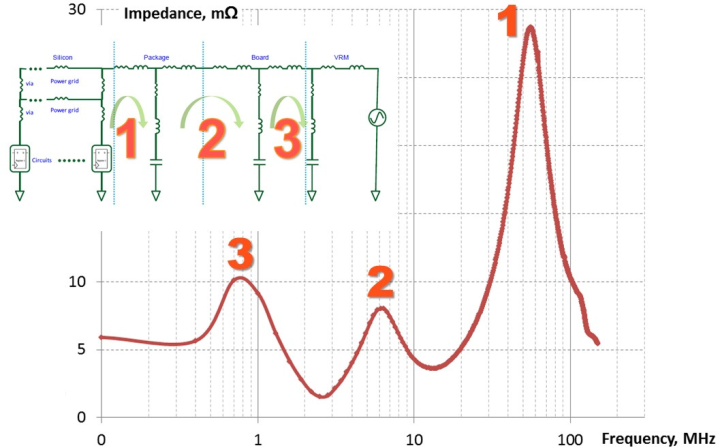

下圖為我們測得的某個系統的阻抗曲線,阻抗曲線有三個明顯的峰值。最主要一個是1\#峰值,大概在50MHz附近,是由片上電容和封裝電感的諧振產生的。2\#峰值在10MH在以下,是由于封裝電容與PCB的電感諧振產生的。最后一個3\#峰值通常都是在1MHz一下的范圍,是由PCB板上小的去耦電容,小的去耦電容與電壓轉換器之間連線的寄生電感的諧振產生的。

實例分析

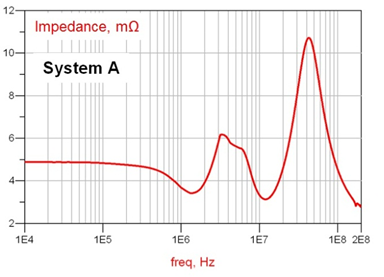

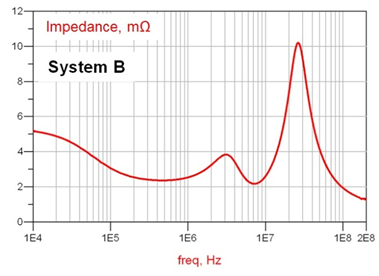

前面進行了理論的分析,現在我們將幾個實例拿來進一步驗證一下我們之前的分析,大家可以參考分析文獻,里面提到了3個系統,3個系統的阻抗曲線分別如下:

系統A和系統B采用相同的芯片設計架構以及相同的生產工藝,均采用Flip chip封裝,所以單位芯片面試的電容容值是相同的,但是系統B的die的面積更大,這樣系統B的on die電容容值更大,是的系統B的一次諧振頻率低,為26MHz,而系統A的一次諧振頻率為38MHz。

系統C是wire bond封裝,封裝上沒有去耦電容,所以系統C就少一個loop,通常表現為一個peak或者2個諧振頻率。另外由于die與PCB去耦電容之間的寄生電感比較大,使得一次諧振頻率變得更低。

總結:

1. 對于flip chip,PCB板級設計幾乎不會影響到一次諧振頻率與幅度

2. 對于wire bond芯片,將去耦電容盡量靠近芯片電源管腳,可以減少die與PCB去耦電容之間的寄生電感,有效的降低系統的阻抗以及提高系統的諧振頻率。

3. 通常情況下芯片的一次諧振頻率處的阻抗最高。

壹芯微科技專注于“二,三極管、MOS(場效應管)、橋堆”研發、生產與銷售,20年行業經驗,擁有先進全自動化雙軌封裝生產線、高速檢測設備等,研發技術、芯片源自臺灣,專業生產流程管理及工程團隊,保障所生產每一批物料質量穩定和更長久的使用壽命,實現高度自動化生產,大幅降低人工成本,促進更好的性價比優勢!選擇壹芯微,還可為客戶提供參數選型替代,送樣測試,技術支持,售后服務等,如需了解更多詳情或最新報價,歡迎咨詢官網在線客服!

手機號/微信:13534146615

QQ:2881579535

工廠地址:安徽省六安市金寨產業園區

深圳辦事處地址:深圳市福田區寶華大廈A1428

中山辦事處地址:中山市古鎮長安燈飾配件城C棟11卡

杭州辦事處:杭州市西湖區文三西路118號杭州電子商務大廈6層B座

電話:13534146615

企業QQ:2881579535

深圳市壹芯微科技有限公司 版權所有 | 備案號:粵ICP備2020121154號