來源:壹芯微 發布日期

2024-04-26 瀏覽:-

來源:壹芯微 發布日期

2024-04-26 瀏覽:-

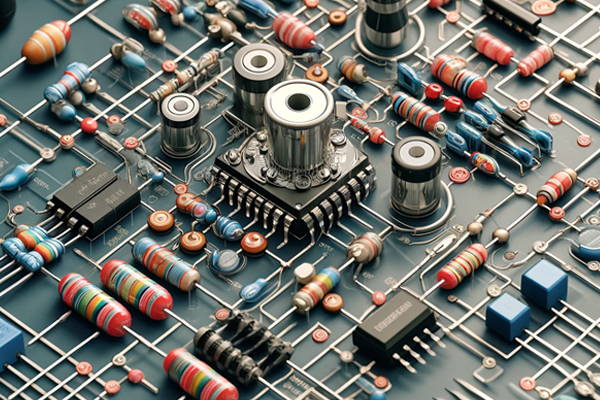

電阻在電路設計中起著重要的電流限制作用,特別是上拉電阻和下拉電阻。這些電阻廣泛應用于系統中,通常被統稱為“拉電阻”。它們的核心功能是將狀態不明的信號線通過電阻拉至高電平(上拉)或低電平(下拉),不同的應用環境對阻值的要求各不相同。

下拉電阻和上拉電阻在電路中有多種用途。首先,它們可以固定開關管關閉時的電路節點電平。例如,當TTL電路驅動CMOS電路時,如果TTL輸出的高電平低于CMOS電路要求的最低高電平,通常需要在TTL輸出端加上拉電阻以提升高電平電壓。此外,OC門電路也必須加裝上拉電阻,以確保輸出端能達到足夠的高電平值。

在實際應用中,例如三極管執行的電平轉換電路,上拉和下拉電阻是不可或缺的。它們還用于穩定輸入管腳的狀態,避免輸入結果不確定或輸出震蕩。比如在CMOS芯片上,為防止靜電破壞,未使用的管腳應接上拉電阻,這有助于降低輸入阻抗并提供一個放電路徑。

關于上拉電阻,它們將電路節點連接至正電源(如Vcc或供電電壓),以保證無外部信號輸入時節點維持高電平(邏輯“1”)。外部設備如果發出邏輯低電平信號,這個信號能夠將節點拉低至邏輯低電平。上拉電阻不僅可以增強輸出引腳的驅動能力,還能提高電壓水平,確保電路的穩定性和可靠性。

對于下拉電阻,它們通過將電路節點連接到地(通常是GND),確保無外部信號輸入時節點保持低電平(邏輯“0”)。這種配置有助于當外部設備發出邏輯高電平時,將節點拉至高電平。下拉電阻同樣重要,以增強電路的穩定性和可靠性。

上拉和下拉電阻的其他應用包括:提高輸出引腳的驅動能力、電阻匹配以減少長線傳輸中的反射波干擾、防止靜電損壞和外部干擾以及在總線如I2C總線上維持空閑時的高電平狀態。它們也用于邏輯IC的管腳懸空處理,確保管腳在不使用時連接到預定電位,以及高速電路中的終端匹配,通過并聯和分壓器端接的方式降低反射波帶來的影響。

工廠地址:安徽省六安市金寨產業園區

深圳辦事處地址:深圳市福田區寶華大廈A1428

中山辦事處地址:中山市古鎮長安燈飾配件城C棟11卡

杭州辦事處:杭州市西湖區文三西路118號杭州電子商務大廈6層B座

電話:13534146615

企業QQ:2881579535

深圳市壹芯微科技有限公司 版權所有 | 備案號:粵ICP備2020121154號