來源:壹芯微 發布日期

2022-01-22 瀏覽:-

來源:壹芯微 發布日期

2022-01-22 瀏覽:-高速緩沖存儲器的作用與原理介紹

在計算機存儲系統的層次結構中,介于中央處理器和主存儲器之間的高速小容量存儲器。它和主存儲器一起構成一級的存儲器。高速緩沖存儲器和主存儲器之間信息的調度和傳送是由硬件自動進行的,程序員感覺不到高速緩沖存儲器的存在,因而它對程序員是透明的。今天將介紹其的作用與工作原理:

1.作用

高速緩沖存儲器(Cache)實際上是為了把由DRAM組成的大容量內存儲器都看做是高速存儲器而設置的小容量局部存儲器,一般由高速SRAM構成。這種局部存儲器是面向CPU的,引入它是為減小或消除CPU與內存之間的速度差異對系統性能帶來的影響。Cache通常保存著一份內存儲器中部分內容的副本(拷貝),該內容副本是最近曾被CPU使用過的數據和程序代碼。

高速緩沖存儲器

在計算機技術發展過程中,主存儲器存取速度一直比中央處理器操作速度慢得多,使中央處理器的高速處理能力不能充分發揮,整個計算機系統的工作效率受到影響。有很多方法可用來緩和中央處理器和主存儲器之間速度不匹配的矛盾,如采用多個通用寄存器、多存儲體交叉存取等,在存儲層次上采用高速緩沖存儲器也是常用的方法之一。很多大、中型計算機以及新近的一些小型機、微型機也都采用高速緩沖存儲器。

高速緩沖存儲器的容量一般只有主存儲器的幾百分之一,但它的存取速度能與中央處理器相匹配。根據程序局部性原理,正在使用的主存儲器某一單元鄰近的那些單元將被用到的可能性很大。因而,當中央處理器存取主存儲器某一單元時,計算機硬件就自動地將包括該單元在內的那一組單元內容調入高速緩沖存儲器,中央處理器即將存取的主存儲器單元很可能就在剛剛調入到高速緩沖存儲器的那一組單元內。于是,中央處理器就可以直接對高速緩沖存儲器進行存取。在整個處理過程中,如果中央處理器絕大多數存取主存儲器的操作能為存取高速緩沖存儲器所代替,計算機系統處理速度就能顯著提高。

2.工作原理

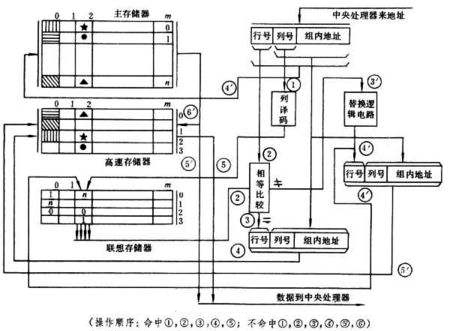

高速緩沖存儲器通常由高速存儲器、聯想存儲器、替換邏輯電路和相應的控制線路組成。在有高速緩沖存儲器的計算機系統中,中央處理器存取主存儲器的地址劃分為行號、列號和組內地址三個字段。于是,主存儲器就在邏輯上劃分為若干行;每行劃分為若干的存儲單元組;每組包含幾個或幾十個字。高速存儲器也相應地劃分為行和列的存儲單元組。二者的列數相同,組的大小也相同,但高速存儲器的行數卻比主存儲器的行數少得多。

高速緩沖存儲器原理圖

聯想存儲器用于地址聯想,有與高速存儲器相同行數和列數的存儲單元。當主存儲器某一列某一行存儲單元組調入高速存儲器同一列某一空著的存儲單元組時,與聯想存儲器對應位置的存儲單元就記錄調入的存儲單元組在主存儲器中的行號。

當中央處理器存取主存儲器時,硬件首先自動對存取地址的列號字段進行譯碼,以便將聯想存儲器該列的全部行號與存取主存儲器地址的行號字段進行比較:若有相同的,表明要存取的主存儲器單元已在高速存儲器中,稱為命中,硬件就將存取主存儲器的地址映射為高速存儲器的地址并執行存取操作;若都不相同,表明該單元不在高速存儲器中,稱為脫靶,硬件將執行存取主存儲器操作并自動將該單元所在的那一主存儲器單元組調入高速存儲器相同列中空著的存儲單元組中,同時將該組在主存儲器中的行號存入聯想存儲器對應位置的單元內。

當出現脫靶而高速存儲器對應列中沒有空的位置時,便淘汰該列中的某一組以騰出位置存放新調入的組,這稱為替換。確定替換的規則叫替換算法,常用的替換算法有:最近最少使用算法(LRU)、先進先出法(FIFO)和隨機法(RAND)等。替換邏輯電路就是執行這個功能的。另外,當執行寫主存儲器操作時,為保持主存儲器和高速存儲器內容的一致性,對命中和脫靶須分別處理

〔壹芯微〕專業研發生產二極管,三極管,MOS管,橋堆,專注領域,專業品質,研發技術-芯片源自中國臺灣,擁有全工序封裝生產線,配備高標準可靠性實驗室,引入國外先進測試儀器,檢測設備,以及專業團隊豐富的生產經驗,保障每個器件的參數和性能的充分穩定性,同時實現了高度全自動化生產,大幅度降低人工成本,并與中國臺灣芯片制造商達成合作,產品低于同行10%,壹芯微還提供有選型替代,技術支持,售后FAE,歡迎點擊頁面右側"在線客服" 咨詢了解產品詳情和最新報價,提供免費樣品送予測試

手機號/微信:13534146615

QQ:2881579535

工廠地址:安徽省六安市金寨產業園區

深圳辦事處地址:深圳市福田區寶華大廈A1428

中山辦事處地址:中山市古鎮長安燈飾配件城C棟11卡

杭州辦事處:杭州市西湖區文三西路118號杭州電子商務大廈6層B座

電話:13534146615

企業QQ:2881579535

深圳市壹芯微科技有限公司 版權所有 | 備案號:粵ICP備2020121154號