收藏壹芯微 | 在線留言| 網(wǎng)站地圖

您好!歡迎光臨壹芯微科技品牌官網(wǎng)收藏壹芯微 | 在線留言| 網(wǎng)站地圖

您好!歡迎光臨壹芯微科技品牌官網(wǎng) 來源:壹芯微 發(fā)布日期

2022-04-21 瀏覽:-

來源:壹芯微 發(fā)布日期

2022-04-21 瀏覽:-AD9854的特點、引腳功能及使用介紹|壹芯微

AD9854數(shù)字合成器是高集成度的器件,它采用先進(jìn)的DDS技術(shù),片內(nèi)整合了兩路高速、高性能正交D/A轉(zhuǎn)換器通過數(shù)字化編程可以輸出I、Q兩路合成信號。在高穩(wěn)定度時鐘的驅(qū)動下,AD9854將產(chǎn)生一高穩(wěn)定的頻率、相位、幅度可編程的正弦和余弦信號,作為本振用于通信,雷達(dá)等方面。AD9854的DDS核具有48位的頻率分辨率(在300M系統(tǒng)時鐘下,頻率分辨率可達(dá)1uHZ)。輸出17位相位截斷保證了良好的無雜散動態(tài)范圍指標(biāo)。AD9854允許輸出的信號頻率高達(dá)150MHZ,而數(shù)字調(diào)制輸出頻率可達(dá)100MHZ。通過內(nèi)部高速比較器正弦波轉(zhuǎn)換為方波輸出,可用作方便的時鐘發(fā)生器。

1.特點與優(yōu)勢

300MHz內(nèi)部時鐘速率;

FSK、BPSK、PSK、線性調(diào)頻、AM操作;

兩個集成式12位數(shù)模轉(zhuǎn)換器(DAC);

超高速比較器,均方根抖動:3ps;

出色的動態(tài)性能:80dBSFDR(100MHz±1MHzAOUT);

4×至20×可編程基準(zhǔn)時鐘乘法器;

兩個48位可編程頻率寄存器;

兩個14位可編程相位偏移寄存器;

12位可編程振幅調(diào)制和開關(guān)輸出形鍵控功能;

單引腳FSK和BPSK數(shù)據(jù)接口;

通過輸入/輸出接口提供PSK功能;

線性或非線性FM線性調(diào)頻功能,具有單引腳頻率保持功能。

2.引腳及功能

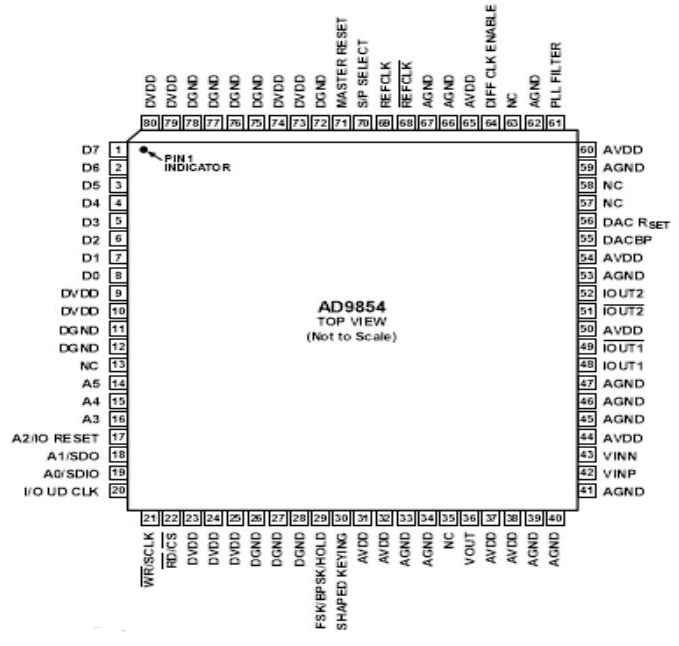

圖1 AD9854引腳排列圖

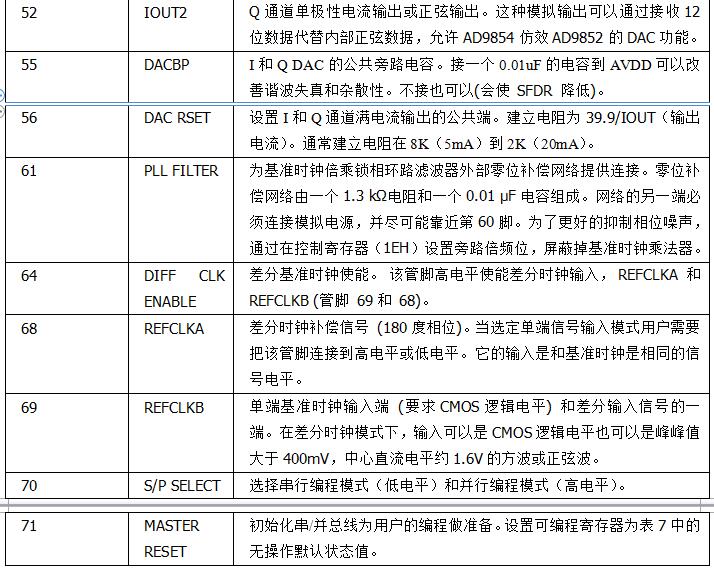

引腳描述:

3.內(nèi)部結(jié)構(gòu)框圖

AD9854內(nèi)部結(jié)構(gòu)框圖

圖2 AD9854內(nèi)部結(jié)構(gòu)框圖

4.結(jié)構(gòu)模塊功能

AD9854采用3.3V單電源供電,允許電源誤差為+5%,最大功耗4.06W。由于整體功耗很大,器件內(nèi)部控制寄存器設(shè)置了可以關(guān)斷比較器、QDAC、數(shù)字部分、PLL、反辛格濾波器等模塊的關(guān)斷位,用戶可以將未使用的模塊關(guān)閉,需要時再打開,減小芯片功耗和發(fā)熱。AD9854的控制接口采用節(jié)省I/O口的2線或3線SPI協(xié)議串行接口和100MHz高速并行接口。AD9854片上重要模塊介紹如下:

4.1DDS核

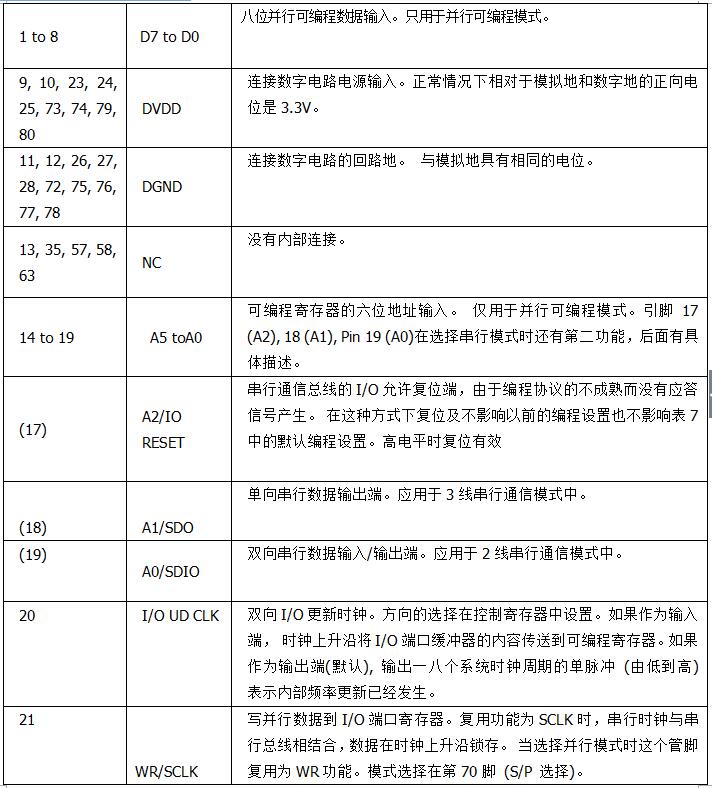

AD9854中的新型高速DDS核提供了48位頻率分辨率,在系統(tǒng)時鐘300MHz的情況下仍能夠精確到1,保持17位即可確保該芯片具有優(yōu)秀的無雜散動態(tài)范圍(SFDR),100MHz()輸出下SFDR達(dá)到80dB。

根據(jù)奈奎斯特采樣定理,在300MHz系統(tǒng)時鐘下,AD9854理論上最高可以輸出150MHz的信號,在實際應(yīng)用中,輸出信號達(dá)到150MHz時,信號質(zhì)量很差,幅度衰減非常大,實際可用最高頻率大概在130MHz左右。AD9854的輸出信號數(shù)字調(diào)諧頻率可以達(dá)到每秒1億次。

4.2雙路正交DAC

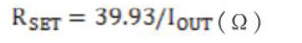

AD9854內(nèi)部有兩路DAC——IDAC和QDAC。兩路DAC的滿量程輸出幅度由第56引腳的電阻——中電流決定,最大不超過20mA,當(dāng)設(shè)置滿量程電流在20mA時可獲得最佳SFDR性能的電流由下式?jīng)Q定:

式中,為輸出滿量程電流。在輸出高頻信號時,總諧波失真變得明顯,雙路DAC的滿量程電流更應(yīng)合理設(shè)置以獲得最佳SFDR。兩路DAC都可以由程序設(shè)定是否經(jīng)過反辛格濾波器。

IDAC內(nèi)部固定于正弦表連接,QDAC可配置為與內(nèi)部余弦表連接或獨立出來,作為一個單獨的高速電流DAC使用,此時QDAC的輸出幅度由用戶寫入的12位二進(jìn)制補碼決定。當(dāng)QDAC不用時可以關(guān)斷以降低功耗。

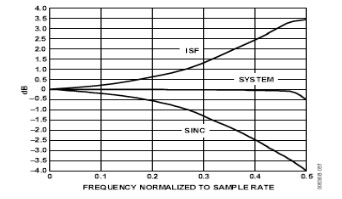

4.3反辛格濾波器(反sinc濾波器)

DDS是靠高速DAC將模擬正弦信號量化輸出的過程,輸出信號是由一個一個小臺階構(gòu)成的。這時信號的頻譜為sinc包絡(luò),由于DAC的零階保持效應(yīng),輸出信號的頻譜為sinc包絡(luò)與脈沖流經(jīng)過付里葉變換的乘積,所以輸出頻譜會有遵從sine響應(yīng)的固有的畸變。反辛格濾波器的頻譜響應(yīng)為反sinc包絡(luò),數(shù)據(jù)經(jīng)過該濾波器就可以校正sinc包絡(luò)形的畸變。反辛格濾波器使得寬帶信號在低頻和高頻使得幅度變化不會太大,如QPSK信號。反辛格濾波器能起到穩(wěn)定幅度的作用,但功耗很大,在300MHz頻率下達(dá)到400mA以上,且會帶來插入損耗。

4.4時鐘倍頻器

AD9854的參考時鐘為300MHz,在最大時鐘頻率下頁能夠精確到1。但是這是基于所提供的時鐘源為高精度時鐘源,如何提供這一高精度、高頻參時鐘是一個不得不解決的問題。

有廠商生產(chǎn)這樣的振蕩器,但性價比太低,一個300MHz的高精度振蕩器不比AD9854便宜。而且300MHz的振蕩信號還很容易耦合到其他電路中,干擾有用信號。為此,AD9854內(nèi)設(shè)了一個4-20倍可編程時鐘倍頻器,用戶可以外接一個高精度、低頻的時鐘源,然后經(jīng)內(nèi)部倍頻后再共給DDS核使用。需要指出的是,AD9854提供兩種時鐘輸入方式——單端輸入和雙端輸入。建議用戶將單端時鐘經(jīng)用變壓器或時鐘芯片(如MC100LVEL16)把單端時鐘轉(zhuǎn)換為差分信號再輸入到DDS芯片,這樣能獲得更好的性能。

4.5調(diào)幅模塊

AD9854在內(nèi)部還集成了調(diào)幅模塊,可以通過程序設(shè)定DAC輸出最大幅度。可以通過高速控制器,如FPGA、DSP對信號進(jìn)行調(diào)幅操作,同時可以用此功能軟件穩(wěn)幅。

4.6比較器

AD9854的片上比較器具有300MHz切換速率、3ps均方根抖動,輸出可以用作其他電路的高精度時鐘源。

5.使用方法

5.1內(nèi)部和外部更新時鐘

這種更新時鐘功能占用一個I/O引腳(20腳)和一個32位可編程減計數(shù)器。為使I/O寄存器的編程對DDS操作有效必須在20腳送外部時鐘信號(由低電平到高電平變化)或使能內(nèi)部的32位更新時鐘。

當(dāng)用戶選擇外部更新時鐘,它的內(nèi)部系統(tǒng)時鐘會防止局部的寄存器的編程變化影響數(shù)據(jù)的建立和有效時間。這種模式可以讓用戶實現(xiàn)對編程信息使能的控制。系統(tǒng)默認(rèn)更新時鐘是內(nèi)部更新,為了切換為外部更新用戶必須將更新時鐘位設(shè)置為邏輯高電平。內(nèi)部更新模式時鐘自動產(chǎn)生,更新脈沖的時間由用戶來設(shè)置。

內(nèi)部更新時鐘的建立通過用戶對32位更新時鐘寄存器和時鐘更新位的邏輯電平來設(shè)置。更新時鐘減計數(shù)器的操作是在系統(tǒng)時鐘的一半速率下進(jìn)行的(最大為150MHZ),并且它是從32位二進(jìn)制值開始減計數(shù)的。當(dāng)計數(shù)值為0時,會在IO更新腳自動產(chǎn)生一個輸出,更新功能實現(xiàn)。在20腳的內(nèi)部和外部的更新時鐘,允許用戶通過設(shè)置更新時鐘速率來同步編程信息。更新脈沖的輸出時間為

(N+1)×(SystemClockPeriod×2)

其中,N是用戶編程設(shè)置的32位有效值。N的范圍是從1到(232−1)的值。內(nèi)部更新時鐘輸出的脈沖會在20腳固定的持續(xù)8個時鐘周期的高電平時間。

對更新時鐘寄存器的值設(shè)置為小于5個時鐘周期會讓IO更新腳持續(xù)輸出高電平,時鐘更新功能仍然有效,但是用戶不能利用該信號來指示數(shù)據(jù)的傳輸。這是IO更新時鐘輸出時的最低高電平持續(xù)時間。

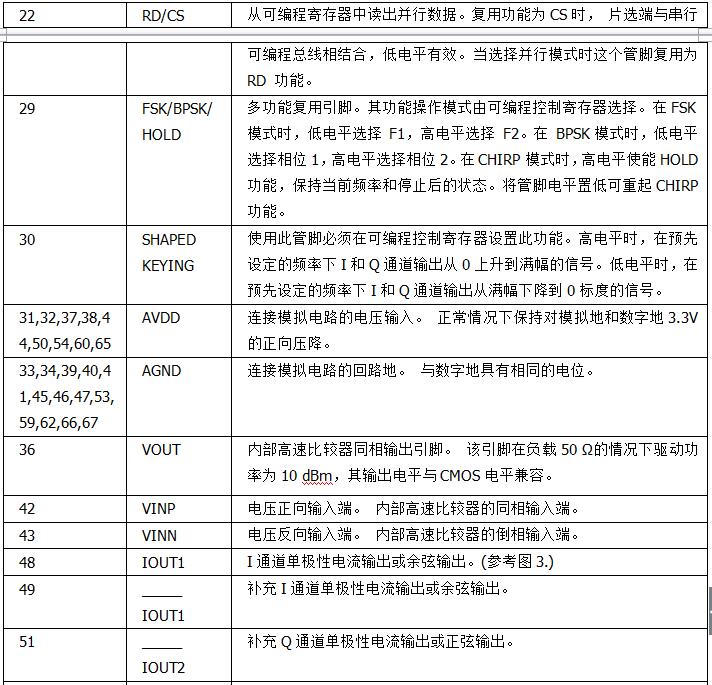

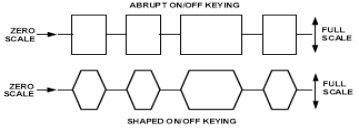

5.2通斷整形鍵控

這一特征允許用戶對I和Q通道輸出的信號進(jìn)行時間——幅度設(shè)置。這一功能在數(shù)據(jù)的突變傳輸中用來減小對頻譜的限制,改善數(shù)據(jù)的傳輸。用戶必須在控制寄存器中將OSKEN位置邏輯高電平來使能數(shù)字乘法器。否則如果OSKEN位為低電平,I和Q通道的輸出為滿幅的信號,數(shù)字乘法器的控制將被旁路掉。除了設(shè)置OSKEN位以外,第二功能位,OSKINT必須設(shè)置為高電平。邏輯高電平將選中內(nèi)部的線性斜率增減控制功能。OSKINT設(shè)置為低電平控制開關(guān)將由原來的數(shù)字乘法器切換到12位可編程幅度寄存器,輸出的幅度在任何模式下都可以動態(tài)的變化。最大輸出幅度是由RSET電阻和OSKINT使能不可編程時決定的。

圖3 通斷整形鍵控

輸出從零幅到滿幅的傳輸時間由用戶通過編程設(shè)置。傳輸時間由兩個固定成員和一個變量成員決定。變量是一個8位斜率計數(shù)器。這是一個減計數(shù)器,它的最大時鐘是系統(tǒng)的最大時鐘(300MHZ),在計數(shù)值為零時,輸出一個脈沖。在脈沖的有效期間,將會發(fā)送一個12位計數(shù)值,它連接到一個12位數(shù)字乘法器。當(dāng)數(shù)字乘法器的輸入值是0時,輸入信號與0相乘,產(chǎn)生一個零幅信號。當(dāng)數(shù)字乘法器的輸入值是1時,輸入信號與4095/4096相乘,產(chǎn)生一個接近滿幅的信號。還有4094個分段的乘數(shù),輸出的幅度由二進(jìn)制數(shù)值決定。

如果減計數(shù)值小于3,則斜率計數(shù)器無效,因此數(shù)字乘法器輸出一個固定幅度的信號。這個停止條件可被用戶利用,來產(chǎn)生OOK信號。

最后,當(dāng)OSKINT位設(shè)置為高電平時,改變30腳的邏輯電平,實現(xiàn)整形鍵控,通過變成可自動完成線性功能。30腳的邏輯高電平會有一個到滿幅的線性輸出并且一直保持直到邏輯電平變?yōu)榈停敵鰰苯抵亮惴?/p>

5.3I和Q通道輸出

正弦和余弦輸出分別由I和Q通道輸出。它們的最大輸出值由56腳的電阻決定,最大輸出電流為20毫安。但是一般都設(shè)置為10毫安輸出,這樣可以有較好的無雜散動態(tài)比。設(shè)置輸出電阻為

RSET=39.93/IOUT

模數(shù)輸出的最大電壓范圍是-0.5V到+1.0V。電壓超出這個范圍會使波形失真,甚至損壞器件。

5.4模數(shù)輸出控制

12位的Q通道輸出可重新配置為控制和輔助的模數(shù)輸出。模數(shù)控制輸出可給外部電路提供直流控制電平,也可輸出交流信號以及控制比較器輸出方波的占空比。當(dāng)控制寄存器(并行地址為:1FH)中的SRCQDAC位設(shè)置為邏輯高電平時,Q通道的模數(shù)輸入由內(nèi)部的12位數(shù)據(jù)切換到外部輸入,輸入的是用戶設(shè)定的兩個12位比較數(shù)據(jù)。數(shù)據(jù)以最大100MHZ的速率通過并行或串行接口送入寄存器。此模數(shù)轉(zhuǎn)換的時鐘是系統(tǒng)時鐘,每秒最多比較300M次,并且它和I通道具有相同的電流輸出能力。

5.5反SINC功能

由正弦查詢表輸出的數(shù)據(jù)將直接輸入到逆sinc函數(shù)(InverseSINCFunction)濾波器。AD9854具有兩個逆sinc函數(shù)濾波器,能夠?qū)π盘栠M(jìn)行sin(x)/x校正,補償DAC輸出頻譜中固有的sin(x)/x滾降(roll2off)效應(yīng),這種校正能夠保證寬帶信號如QPSK(四相制移相鍵控信號),在從DAC輸出時,幅度不會隨著頻率變化而產(chǎn)生突變。由逆sinc函數(shù)濾波器輸出的信號將會乘上1個衰減因子,然后再送入到D/A的轉(zhuǎn)換器。通過配置I、Q支路AM調(diào)整寄存器,用戶可以設(shè)置這個衰減因子的大小,該寄存器為12Bit,衰減因子的數(shù)值范圍是0~4095/4096。例如,當(dāng)AM調(diào)整寄存器設(shè)置為200時,衰減因子則為:200/4096。此外,當(dāng)開/關(guān)成形鍵控管腳被設(shè)置為1時,AM調(diào)整寄存器還可設(shè)定信號幅度由0到峰值的轉(zhuǎn)換時間。在數(shù)據(jù)突變傳輸情況下,該功能會有效緩解頻譜沖擊和數(shù)據(jù)突變給信號生成帶來的不利影響。數(shù)字信號經(jīng)過生成、查表、濾波、衰減,最終送入到D/A轉(zhuǎn)換器。

5.6基準(zhǔn)時鐘乘法器

基準(zhǔn)時鐘乘法器是一個允許用戶編程的,內(nèi)置基于鎖相環(huán)(PLL)的可編程參考時鐘倍乘器,倍乘范圍為4倍到20倍。使用該功能允許用戶僅僅輸入15MHZ的參考時鐘產(chǎn)生300MHZ的內(nèi)部系統(tǒng)時鐘。

AD9854的參考時鐘功能能允許從外部時鐘源輸入的直接時鐘。AD9854的系統(tǒng)時鐘可以是參考時鐘倍頻器的輸出(如果被允許的前提下),也可以是參考時鐘輸入,REFCLK可以是single-ended或differented輸入,由引腳64DIFFCLKENABLE的設(shè)置確定,分別是低或高電平控制。

圖4 反辛格濾波器效果圖

5.7倍頻范圍位

倍頻范圍位決定通過倍頻之后的時鐘范圍。當(dāng)倍頻位設(shè)定為高電平操作時鐘從200MHZ到300MHZ(內(nèi)部系統(tǒng)時鐘速率)。當(dāng)倍頻位設(shè)定為低電平操作時鐘為200M以下。倍頻范圍位改變鎖相環(huán)的參數(shù)來改善頻率范圍內(nèi)的最佳相位噪聲。

5.861腳,倍頻濾波

該引腳提供連接到PLL環(huán)路濾波器的外部0補償網(wǎng)絡(luò)。0補償網(wǎng)絡(luò)由1.3KΩ的電阻和0.01uF的電容串聯(lián)組成。網(wǎng)絡(luò)的另一端應(yīng)該盡可能近地連接到引腳60,AVDD。為了達(dá)到最佳的噪聲效果,始終倍頻器應(yīng)該被分路,通過在控制寄存器IE地址中設(shè)置旁路倍頻位。

5.9差分時鐘使能

這是一個可編程PLL-based參考時鐘倍頻器,其允許用戶從4倍到20倍間選擇整數(shù)倍的時鐘。使用該功能允許用戶僅僅輸入15MHZ的參考時鐘產(chǎn)生300MHZ的內(nèi)部系統(tǒng)時鐘。

AD9854的參考時鐘功能能允許從外部時鐘源輸入的直接時鐘。AD9854的系統(tǒng)時鐘可以是參考時鐘倍頻器的輸出(如果被允許的前提下),也可以是參考時鐘輸入,REFCLK可以是single-ended或differented輸入,由引腳64DIFFCLKENABLE的設(shè)置確定。分別是低或高電平控制。

對于信號單端輸入方式,REFCLKB管腳接電源或地;對于差分輸入方式,輸入端信號可以是方波或正弦波,直流電平大約為1.6V,峰峰值大于0.4V。

高速比較器——最優(yōu)化的最高速速度大于300MHZ的反復(fù)速率,低抖動,靈敏的輸入,built-in滯后,輸出最小為1皮法的電平,連接到50歐姆的負(fù)載或CMOS邏輯電平,連接到高阻抗負(fù)載。比較起能從節(jié)電模式到受保護電壓之間分離。比較器使用于“時鐘發(fā)生器”的應(yīng)用,把DDS產(chǎn)生的濾波后的正弦波形變成方波。

6.編程

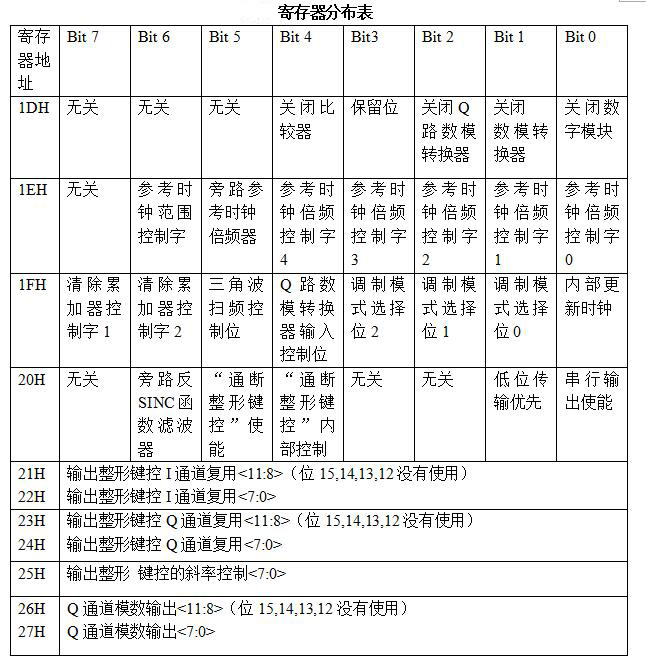

AD9854的各寄存器列出在下表,包含各各功能的片內(nèi)編程信息。很多應(yīng)用要求很小的編程規(guī)模去裝配AD9854,就可以使用了,實現(xiàn)功能了。但有一些要求用戶使用所有的12個寄存器入口地址。AD9854支持8位并行I/O操作或一位SPI-compaTIble串行I/O操作。所有入口寄存器能讀和寫,在每個I/O操作模式下。S/P選擇,引腳70,用于I/O模式選擇。若系統(tǒng)使用并行I/O模式,必須連接S/P選擇引腳到VDD。若系統(tǒng)操作在串行模式,必須連接S/P選擇引腳到GND。

(1)不使用模式,I/O口數(shù)據(jù)寫入緩沖寄存器,不影響該部分操作直到緩沖寄存器傳輸數(shù)據(jù)到寄存器數(shù)據(jù)庫。信息傳輸同時產(chǎn)生在系統(tǒng)時鐘,兩種產(chǎn)生方式:

1)內(nèi)部控制在某一由用戶編程產(chǎn)生的速率

2)由用戶外部控制,I/O操作能在沒有REFCLK情況下進(jìn)行,但數(shù)據(jù)從緩沖期傳輸?shù)酱鎯ζ鳎瑳]有REFCLK是不行的。能從該文獻(xiàn)更新時鐘章節(jié)中了解到更多的詳細(xì)信息。復(fù)位管理——邏輯高電平有效,必須保證電平不小于10個系統(tǒng)時鐘周期的持續(xù)時間。復(fù)位主要引起通信總線的初始化并載入默認(rèn)值到內(nèi)部或外部的時鐘更新段。

(2)并行輸入輸出操作

在S/P選擇引腳被拉為高電平時,并行輸入輸出模式被激活。這種輸入輸出口與標(biāo)準(zhǔn)工業(yè)DSPs和microcontrollers相兼容。6個地址位,8個雙向數(shù)據(jù)位,和分離的寫/讀控制輸入來補足這輸入輸出口引腳。

并行輸入輸出操作模式允許到1/10.5納秒對每個寄存器進(jìn)行單字節(jié)操作。對寄存的回讀操作主要用來優(yōu)化對AD9854的設(shè)計(讀寄存器不能保證100MHz的操作速度,這一點他們?yōu)橹皇擒浖{(diào)試準(zhǔn)備的)。

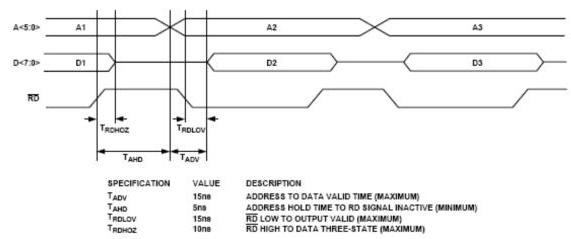

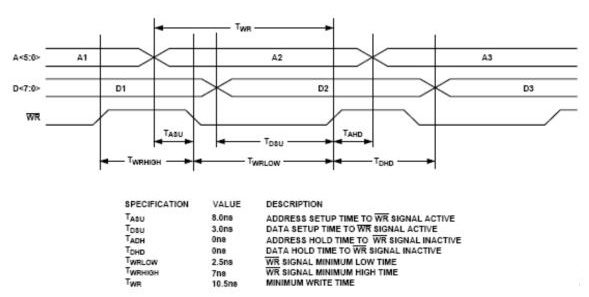

并行輸入輸出操作時序圖如圖5和圖6所示。

圖5 并行操作讀時序圖

圖6 并行操作寫時序圖

以上就是AD9854的特點、引腳功能及使用的介紹了。AD9854與AD9852單信號音頻率合成器之間具有引腳兼容性,可在−40°C至+85°C的擴展工業(yè)溫度范圍內(nèi)工作。目前AD9854可在捷變正交LO頻率合成、可編程時鐘發(fā)生器、雷達(dá)和掃描系統(tǒng)的FM線性調(diào)頻源、測試與測量設(shè)備等領(lǐng)域中使用。

深圳壹芯微科技,20年專業(yè)生產(chǎn)“二極管、三極管、場效應(yīng)管、橋堆”等,專業(yè)生產(chǎn)管理團隊對品質(zhì)流程嚴(yán)格管控,超過4800家電路電器生產(chǎn)企業(yè)選用合作,價格低于同行(20%),更具性價比,提供選型替代,送樣測試,數(shù)據(jù)手冊,技術(shù)支持,售后FEA,如需了解更多詳情或最新報價,歡迎咨詢官網(wǎng)在線客服!

手機號/微信:13534146615

QQ:2881579535

壹芯微首頁 場效應(yīng)管 貼片二極管 榮譽認(rèn)證 直插二極管 網(wǎng)站地圖 三極管 聯(lián)系壹芯微

工廠地址:安徽省六安市金寨產(chǎn)業(yè)園區(qū)

深圳辦事處地址:深圳市福田區(qū)寶華大廈A1428

中山辦事處地址:中山市古鎮(zhèn)長安燈飾配件城C棟11卡

杭州辦事處:杭州市西湖區(qū)文三西路118號杭州電子商務(wù)大廈6層B座

電話:13534146615

企業(yè)QQ:2881579535

深圳市壹芯微科技有限公司 版權(quán)所有 | 備案號:粵ICP備2020121154號